Now Develop IoT Applications with ARIES IoT v1.0 Board Based on THEJAS32 RISC-V SoC from C-DAC

India’s C-DAC announces the new IoT targeted development board powered by indigenously developed RISC-V SoC THEJAS32. The board combines Wi-Fi and other embedded sensors.

RISC-V for semiconductors is what Linux is for software. Pronounced as “risk five”, it is an open-source Instruction Set Architecture (ISA) initially developed by the University of California, Berkeley. An ISA is the foundational design of a modern microprocessor that ends up crunching numbers inside all of the smart devices we use today. A few known examples of ISA are x86, ARM32, AVR etc, which are all proprietary architectures. Even though processors with these proprietary architectures are well-performing and cost-effective, their original designs remain closed-source or protected by IPs for which you will need to pay hefty licensing fees. This effectively prevents any semiconductor “newbie” from designing their own chips and mass manufacturing them, which is one of the reasons why the microprocessor market is dominated by a handful of companies. In a highly digital and connected “one world”, the capability to design and manufacture semiconductor products is getting enough recognition as a matter of national security. Thanks to COVID-19 and the global semiconductor shortage followed by it, which helped to bolster that realization.

More countries are now trying to develop semiconductor chips for their own domestic use. But in order to save the R&D costs and not reinvent the wheels, new players need to start somewhere above zero. That’s where open architectures like the RISC-V come to play. RISC-V is one of the many open ISAs out there but it has been growing in popularity than the competing ones. We are seeing more and more semiconductor companies and state-funded firms developing and manufacturing microprocessors based on RISC-V. The tried and tested designs that offer competitive performance and zero license fees save a lot of time and cost on R&D.

India is a country that also doesn’t want to be left behind in this race for semiconductor mastery. That’s why under the supervision of the Centre for Development of Advanced Computing (C-DAC), a government-funded autonomous entity, India is developing RISC-V-based microprocessors. The VEGA is a family of RISC-V SoCs being developed by C-DAC and they have released their latest development board called ARIES IoT V1 which combines a THEJAS32 SoC and a Wi-Fi module.

VEGA Microprocessors

India has been taking steps and making important decisions to domesticate the semiconductor industry for a while now. Attracting established foreign companies to set up semiconductor manufacturing units in India is one of those steps which is seeing progress in recent months with companies like Vedanta and Tata making the headlines. Simultaneously, India is also developing microprocessors based on RISC-V. India imports almost 100% of its semiconductor consumables from outside and the govt wants to reduce that dependability. India is already a significant player when it comes to semiconductor design and verification. Many international companies have design houses in India that tap the intellectual resources India is good at producing. Indian companies like Si2 Microsystems, Signalchip, Saankhya Labs, Tessolve, etc. have taken steps in the direction of chip designing, manufacturing, and/or providing semiconductor services. Although these companies started in the 1990s, C-DAC has been operating since 1998, under MeitY, Government of India. C-DAC was realized with the aim to develop supercomputers in India. It was considered the initial phase of domesticating computing power. In the second phase, C-DAC has undertaken the task to design a family of microprocessors, SoCs, IPs, and the supporting ecosystem.

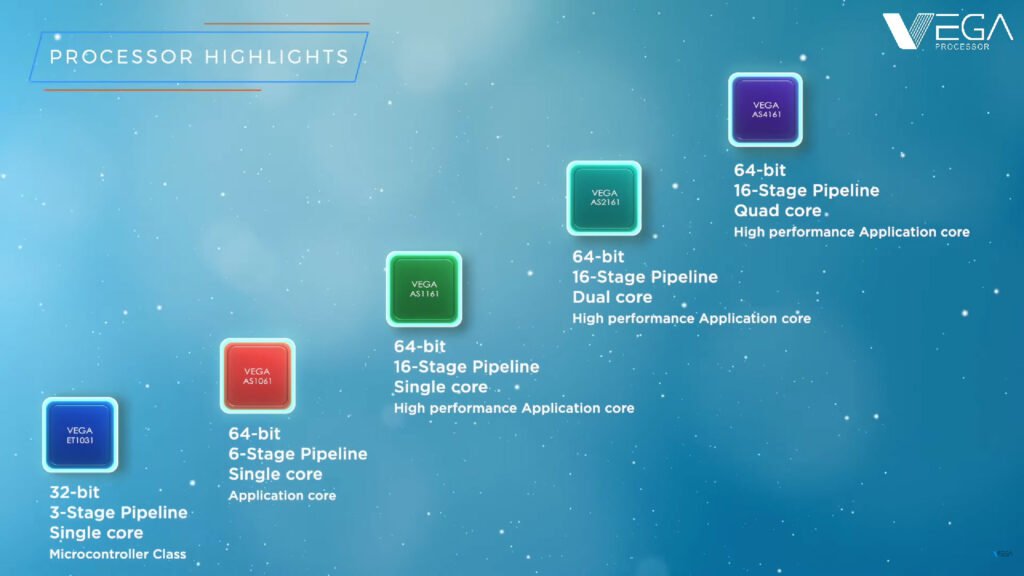

The first step called the Microprocessor Development Programme (MDP) aimed at designing a family of microprocessors called “VEGA” was started in 2015. By 2020, the project in charge said that a series of high-performance 32-bit Single-core (In-order), 64-bit Single-core (In-order & Out-of-order), 64-bit Dual-core (Out-of-order), and 64-bit Quad-core (Out-of-order) designs had been successfully designed and developed. India has also launched an initiative called Digital India RISC-V (DIR-V) program where RISC-V instruction set architecture (ISA) is to be used to develop the indigenous microprocessors. RISC-V has many advantages over the Intel x86 and AMD like, openness, modularity, simplicity, clean-slate design, stability, extensibility, etc, and is a strong competitor to the ARM category of ISAs. India is putting the initiative under the “Atmanirbhar Bharat”, the ambition to domestically produce everything.

| Key Features | VEGA ET1031 | VEGA AS1061 | VEGA AS1161 | VEGA AS2161 | VEGA AS4161 |

|---|---|---|---|---|---|

| RISC-V ISA | 32-bit RV32IM | 64- bit RV64IMAFDC | 64-bit RV64IMAFD | 64-bit RV64IMAFD | 64-bit RV64IMAFD |

| No of cores | 1 | 1 | 1 | 2 | 4 |

| Pipeline | In-order | In-order | Out-of-Order | Out-of-Order | Out-of-Order |

| Pipeline stages | 3-Stage | 6-Stage | 13-16 Stage | 13-16 Stage | 13-16 Stage |

| Superscalar | No | No | Yes | Yes | Yes |

| Processor modes | Machine | Machine/ Supervisor/User | Machine/ Supervisor/User | Machine/ Supervisor/User | Machine/ Supervisor/User |

| MMU | Optional | Yes | Yes | Yes | Yes |

| Debug | Optional | Yes | Yes | Yes | Yes |

| Branch Predictor | No | Yes | Yes | Yes | Yes |

| L1 ICache | TIM | 8KB | 32KB | 32KB | 32KB |

| L1 DCache | TIM | 8KB | 32KB | 32KB | 32KB |

| L2 Caches | No | No | No | 512KB | 1024KB |

| Bus Interface | AHB/AXI4 | AHB/AXI4 | AHB/AXI4/ACE | AHB/AXI4/ACE | AHB/AXI4/ACE |

| IEEE 754-2008 compliant FPU | No | Single and Double precision | Single and Double precision | Single and Double precision | Single and Double precision |

| Availability | Now | Now | Now | Now | Now |

THEJAS32

THEJAS32 is an SoC (System on Chip) built around the VEGA ET1031, a compact and efficient 3-stage in-order 32-bit RISC-V processor core. As the name indicates, it’s a 32-bit high-performance microcontroller that also combines the remaining necessities for an SoC like, memory, peripherals, and clock. This SoC has gained popularity after the Swadeshi Microprocessor Challenge conducted by the government and the Vegathon event took place in October 2022. Multiple companies and individuals participated in the challenges as early adopters to test the new processors. In addition to the 32-bit ones, C-DAC also has 64-bit equivalents like the VEGA AS1061 of their processors intended for the high-performance market.

VEGA ET1031

The key features of the VEGA ET1031 processor core are,

- RISC-V (RV32IM) Instruction Set Architecture

- 3-stage in-order pipeline implementation

- Harvard architecture (separate instruction and data buses)

- High-performance multiply/divide unit

- Configurable AXI4 or AHB external interface

- Optional MPU (Memory Protection Unit)

- Platform Level Interrupt Controller

- Up to 127 IRQs

- Low interrupt latency

- Vectored interrupt support

- Advanced Integrated Debug Controller

- Debug extension allowing Eclipse debugging via a GDB–openOCD–JTAG connection

Specifications

The key specs of the THEJAS32 SoC are,

- 32-bit Single-core RISC-V

- Clock Speed: 100 MHz

- 256 KB SRAM

- Upto 16 MBit Flash

- 8x PWM pins

- 4x Analog input pins

- 3x SPI

- 3x UART

- 2x I2C

- Upto 25 GPIOs

- Input Voltage: 7-12V

- DC Current per I/O Pin: 12 mA

- IO Voltage: 3.3 V

- Package: LQFP 128

C-DAC has not released a detailed and proper datasheet of the SoC yet due to which many of the specifics of the features are not yet known.

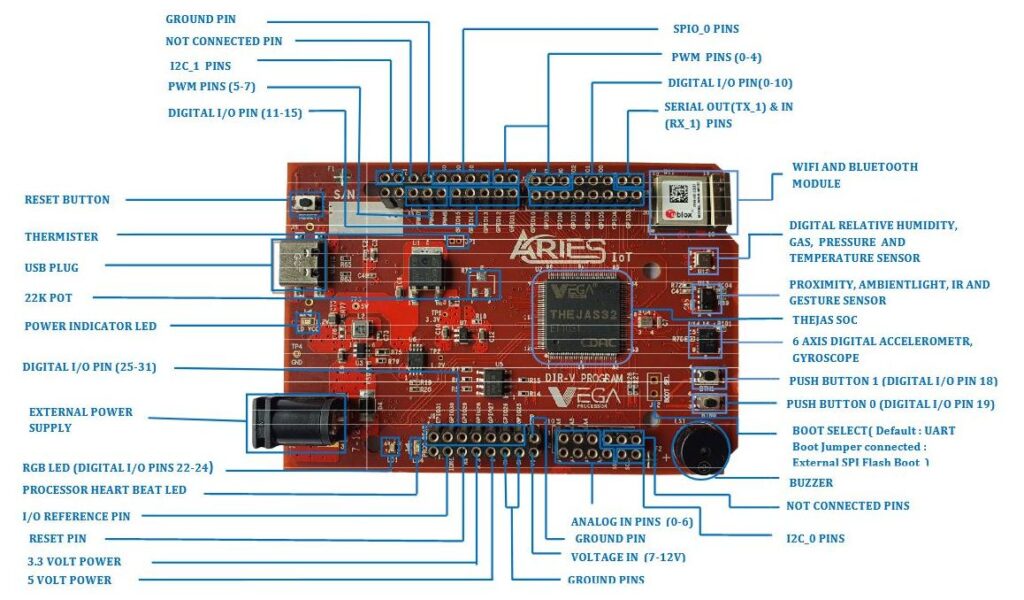

ARIES Family

ARIES is a family of development boards designed by C-CAD for evaluating the THEJAS32 SoC for different applications in the domain of the Internet of Things (IoT), Industrial Control, Automation, etc. There are three boards available in this series, named ARIES MICRO v1.0, ARIES v2.0, and ARIES IoT v1.0. All of the boards use the same SoC but come in different form factors. The ARIES IoT v1.0 combines the NINA-W10 (based on ESP32) wireless module for wireless connectivity and a few other sensors. This board is meant for faster IoT application development. Power can be supplied through the USB-C connector or the DC barrel jack. There is also a buzzer and push buttons for generic inputs and outputs.

Features & Specs

- Single-core THEJAS32 SoC with VEGA ET1031 microprocessor

- 2MB Flash

- 256KB SRAM

- Input Voltage: 7-12V

- DC Current per I/O Pin: 12 mA

- IO Voltage: 3.3 V

- NINA-W102-01B Wi-Fi & Bluetooth module

- APDS-9960 Proximity, ambient light, IR, and gesture sensor

- BME680 humidity and temperature sensor

- BMI088 6-axis inertial measurement unit

The software development support for the THEJAS32 SoCs and the board based on it is given as an online documentation by C-DAC and the SDK and examples codes are located in a Gitlab repository. But you need to request access before you can see all the files. The samples of THEJAS32 series SoCs and development boards are currently only handed out to select institutions, companies, and individuals. So you need to wait for some time before you can buy one from the open market.

Links

- ARIES IoT V1 – C-DAC

- ARIES IoT Datasheet [PDF]

- VEGA Series Documentation

- VEGA ET1031

Short Link

- Short URL to this page – https://circuitstate.com/ariesiot